The NXP {cpu-family} CPU has five GPIO ports. Each port can generate and control 32 signals.

The MCA also features a number of GPIO pins (multiplexed with Analog-to-Digital Converter (ADC) functionality). See MCA I/O pads for a list of all available MCA IOs and their capabilities.

GPIOs on the ConnectCore 8M Mini platforms

-

On the ConnectCore 8M Mini system-on-module:

-

Many of the {cpu-family} GPIOs are available at the system-on-module, multiplexed with other functions (labeled GPIOx_IOy where x is the port and y is the GPIO pin). See Hardware reference manuals for information about GPIO pins and their multiplexed functionality.

-

15 MCA GPIO pins are available (labeled MCA_IOx where x is the GPIO pin).

-

-

On the ConnectCore 8M Mini Development Kit, the expansion connectors allow direct access to some of the {cpu-family} GPIOs.

GPIOs on the SOM and carrier board are used for many purposes, such as:

-

Power enable line for transceivers

-

Reset line for controllers

-

LCD backlight control

-

Interrupt line

-

User LED

-

User button

Kernel configuration

Support for {cpu-family} GPIOs is automatically provided through the non-visible option CONFIG_GPIO_MXC.

Kernel driver

The driver for the {cpu-family} GPIO is located at:

| File | Description |

|---|---|

{cpu-family} GPIO driver |

Device tree bindings and customization

The {cpu-family} GPIO device tree binding is documented at

Documentation/devicetree/bindings/gpio/fsl-imx-gpio.txt.

One GPIO controller is defined for each {cpu-family} GPIO port in the common {cpu-family} device tree file:

gpio1: gpio@30200000 {

compatible = "fsl,imx8mm-gpio", "fsl,imx35-gpio";

reg = <0x0 0x30200000 0x0 0x10000>;

interrupts = <GIC_SPI 64 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 65 IRQ_TYPE_LEVEL_HIGH>;

gpio-controller;

#gpio-cells = <2>;

interrupt-controller;

#interrupt-cells = <2>;

};

[...]

gpio5: gpio@30240000 {

compatible = "fsl,imx8mm-gpio", "fsl,imx35-gpio";

reg = <0x0 0x30240000 0x0 0x10000>;

interrupts = <GIC_SPI 72 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 73 IRQ_TYPE_LEVEL_HIGH>;

gpio-controller;

#gpio-cells = <2>;

interrupt-controller;

#interrupt-cells = <2>;

};The ConnectCore 8M Mini device tree include file and the carrier board device tree files use the {cpu-family} GPIOs.

For example, on the ConnectCore 8M Mini, GPIO3_IO08 is used as the MCA interrupt line, and GPIO1_IO4 is used to activate internal circuitry during the MCA firmware update:

mca_cc8m: mca@63 {

compatible = "digi,mca-cc8m";

reg = <0x63>;

interrupt-parent = <&gpio2>;

interrupts = <10 IRQ_TYPE_LEVEL_HIGH>;

interrupt-controller;

#interrupt-cells = <2>;

fw-update-gpio = <&gpio1 5 GPIO_ACTIVE_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_mca_cc8m>;

[...]

};For example, on the ConnectCore 8M Mini Development Kit, GPIO5_IO3 is used to reset the PHY of ENET1 Ethernet interface:

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec1_gpio>,

<&pinctrl_fec1>;

phy-mode = "rgmii-id";

phy-handle = <ðphy0>;

digi,mdio-lt-supply = <®_1v8_ext>;

phy-supply = <®_3v3_eth0>;

phy-reset-gpios = <&gpio5 3 GPIO_ACTIVE_LOW>;

phy-reset-duration = <1>;

digi,phy-reset-in-suspend;

fsl,magic-packet;

status = "okay";

[...]

};IOMUX configuration

You must configure the pads that are to be used as {cpu-family} GPIOs. See Pin multiplexing (IOMUX).

For GPIOs that are managed by other drivers, you must configure their pad IOMUX inside the driver node specific pinctrl-0 to work according to the specified interface functionalities.

On the ConnectCore 8M Mini example from above, mca_cc8m node configures pinctrl_mca_cc8m:

pinctrl_mca_cc8m: mcagrp {

fsl,pins = <

/* MCA_nINT */

MX8MM_IOMUXC_SD1_RESET_B_GPIO2_IO10 0x56

/* MCA_FW_UPDATE */

MX8MM_IOMUXC_GPIO1_IO05_GPIO1_IO5 0x16

>;

};For GPIOs that are not associated with any interface or that can’t be handled by a driver, see Configure independent pin IOMUX and pad control. The following external pads are configured as GPIOs on the default device tree:

-

On the ConnectCore 8M Mini Development Kit J46 expansion connector:

Pad Signal GPIO 3

GPIO1_IO10

GPIO1_IO10

4

GPIO1_IO15

GPIO1_IO15

5

GPIO1_IO11

GPIO1_IO11

7

GPIO1_IO13

GPIO1_IO13

9

GPIO1_IO14

GPIO1_IO14

-

On the ConnectCore 8M Mini Development Kit J48 expansion connector:

Pad Signal GPIO 5

EXP_I2C_IRQ_N

GPIO5_IO27

7

EXP_I2C_GPIO

GPIO5_IO26

-

User LED 3 is GPIO2_IO19

-

User button 2 is GPIO2_IO20

GPIO pads power domains

The {cpu-family} GPIOs are configurable and can work at 1.8 V or 3.3 V depending on the power domain of the pad they are on.

You can access the GPIOs from your Android application. See GPIO API for more information about the GPIO APIx.

To determine the working voltage of a given GPIO:

-

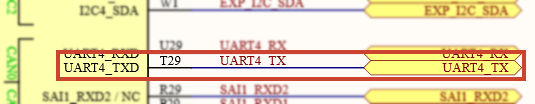

Locate the pad of a given signal on the ConnectCore 8M Mini Development Kit schematics. For instance, on the ConnectCore 8M Mini Development Kit, signal

UART4_TXcomes from padUART4_TXDof the ConnectCore 8M Mini SOM:

-

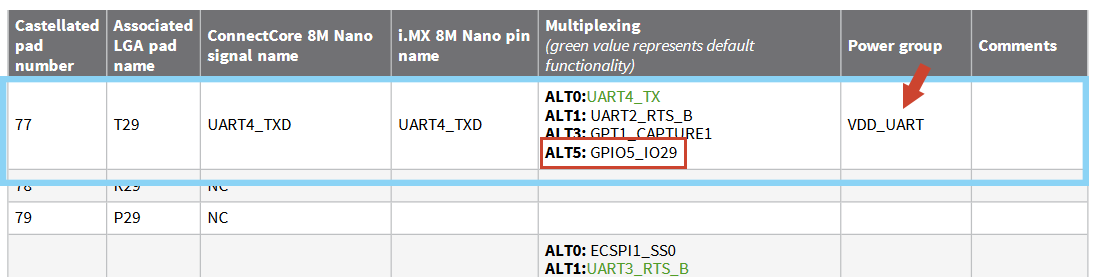

Locate this pad on the IMOUX section of the ConnectCore 8M Mini Hardware Reference Manual. This table lists the associated GPIO of the pad, and the power domain it is on:

-

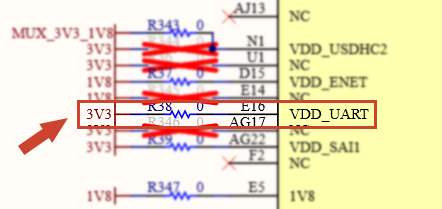

Locate the power domain (

VDD_UARTon the example) on the ConnectCore 8M Mini Development Kit schematics. Here you can tell the voltage of the power domain:

Using the GPIOs

You can access the GPIOs from your Android application. See GPIO API for more information about the GPIO APIx.

Calculate the Linux GPIO number of a GPIO pin

For each GPIO controller entry on the device tree, Linux creates an entry /sys/class/gpio/gpiochipN, where N is an integer number starting at 0, with the following read-only attributes:

-

base: same as N, the first GPIO managed by this chip

-

label: provided for diagnostics (not always unique)

-

ngpio: the number of GPIOs this controller manages (from N to N + ngpio - 1)

GPIOs on the ConnectCore 8M Mini system-on-module

Every GPIO port of the {cpu-family} CPU is a different GPIO controller and thus has its own /sys/class/gpio/gpiochipN entry on the sysfs.

On the default ConnectCore 8M Mini system-on-module device tree, the {cpu-family} CPU’s GPIO ports are probed first:

-

PORT1:

/sys/class/gpio/gpiochip0 -

PORT2:

/sys/class/gpio/gpiochip32 -

PORT3:

/sys/class/gpio/gpiochip64 -

PORT4:

/sys/class/gpio/gpiochip96 -

PORT5:

/sys/class/gpio/gpiochip128

Calculate the Linux GPIO number for a certain GPIO pin by adding the GPIO pin index to the port base index. For instance:

{cpu-family} GPIO2_IO4 (port 2, pin 4) is: 32 + 4 = 36

Since the {cpu-family} CPU has five ports, all of which have 32 pins, the following formula also applies to {cpu-family} CPU GPIOs (without requiring the user to know the GPIO base of each port):

\$"LinuxGPIO_num" = ("<port_index>" - 1) * 32 + "<gpio_pin>"\$

For example, {cpu-family} GPIO2_IO4 (port 2, pin 4) translates to:

\$(color(red)(2) - 1) * 32 + color(red)(4) = 36\$

Sample application

The GPIO Sample Application demonstrates the usage of the GPIO API. In this example, one GPIO is configured as input and another as output. You can press the virtual button to switch on and off the User 0 LED corresponding to the output GPIO.

Go to GitHub to see the application instructions and source code.

See MCA General Purpose Input/Output (GPIO) for additional information on MCA GPIOs.